L'Apple M5 serait entrée en production, selon diverses rumeurs. La version de base de la puce d'Apple, qui pourrait trouver sa place assez rapidement dans des iPad, resterait gravée en 3 nm, mais avec une version un peu plus avancée de la technologie de TSMC (N3P), qui améliorerait les performances de 5 % (nous parlons ici de la fréquence, pas des performances stricto sensu) avec une efficacité améliorée de 5 à 10 %.

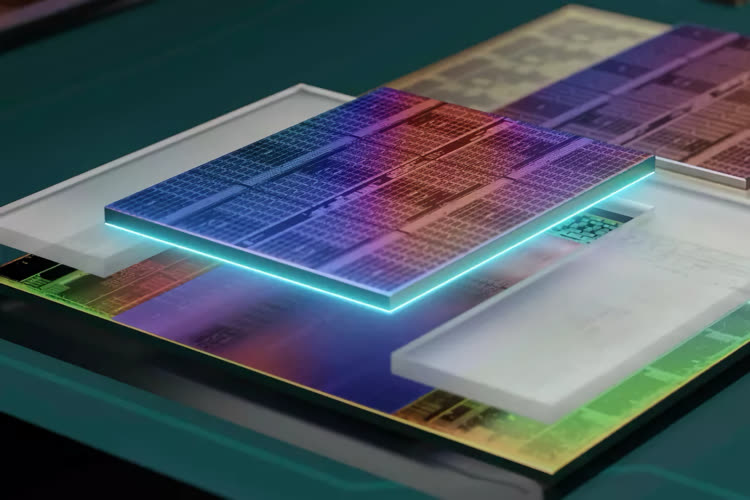

ETNews (en coréen) semble par ailleurs confirmer deux rumeurs récurrentes. La première serait que la puce M5 emploierait bien la technologie « 3D » de TSMC, connue sous le nom de SoIC (System on Integrated Chip). Elle permet d'empiler directement des composants pour — par exemple — rapprocher encore un peu plus la mémoire du système sur puce ou ajouter de la mémoire cache (comme chez AMD). Apple pourrait suivre cette voie en augmentant à moindres frais la capacité du cache SLC1 — System Level Cache —, ce qui permettrait d'améliorer significativement les performances sur les calculs liés à l'IA, très friands d'une bande passante mémoire élevée.

La technologie « 3D » de TSMC pourrait trouver sa place dans les Apple M5

La rumeur confirme aussi implicitement en partie une chose : les versions Pro, Max et probablement Ultra de la puce M5 pourraient partir sur une autre conception. Actuellement, toutes les puces Apple sont monolithiques (même si les variantes Ultra sont composées de deux puces M concaténées), une voie qui commence à atteindre ses limites. Divers bruits de couloirs indiquent que les puces M5 Pro et M5 Max pourraient employer une conception en chiplets, qui consiste à séparer certains éléments du système sur puce pour les produire séparément. Cette solution a l'avantage de permettre un meilleur rendement à la production, tout en offrant un peu plus de flexibilité sur la segmentation des puces. AMD l'utilise sur les Ryzen de bureau depuis quelques années avec succès, et les derniers CPU Intel sont aussi de ce type.

Avec les M5 Pro, Apple pourrait séparer CPU et GPU dans une conception 3D

-

Le cache SLC des systèmes sur puce n'a pas de rapport avec le cache pseudo SLC des SSD, mais le sigle est le même. ↩︎