Avec son processus de fabrication N3, communément qualifié de « gravure à 3 nm », TSMC joue gros. Contrairement au N4 qui n’était qu’une évolution marketing de la gravure à 5 nm, le N3 promet de marquer une nouvelle étape. Il faut dire que la première entreprise qui devrait en profiter n’est autre qu’Apple, avec la puce A17 du prochain iPhone et les puces M3 des prochains Mac et iPad.

Le logo de TSMC au wafer stylisé. Image MacGeneration.

Le logo de TSMC au wafer stylisé. Image MacGeneration.Dans un long article, les spécialistes de WikiChip donnent pas mal d’informations sur ce nouveau procédé. Il s’intéresse particulièrement au processus N3B, pour « base », la première variante de la gravure à 3 nm. TSMC proposera plusieurs versions du processus N3 : une carte graphique qui va demander des centaines de watts n’a pas les mêmes besoins qu’un smartphone, pour lequel la consommation est une contrainte forte.

TSMC : le 3 nm va évoluer, le 2 nm en embuscade

WikiChip rappelle que TSMC est (presque) dans les temps, ce qui n’est pas une évidence dans le monde de la gravure des puces. Le fondeur taiwanais avait annoncé une production en masse au second semestre 2022 et elle a été lancée le 29 décembre 2022… Maintenant, attention, nous allons parler technique.

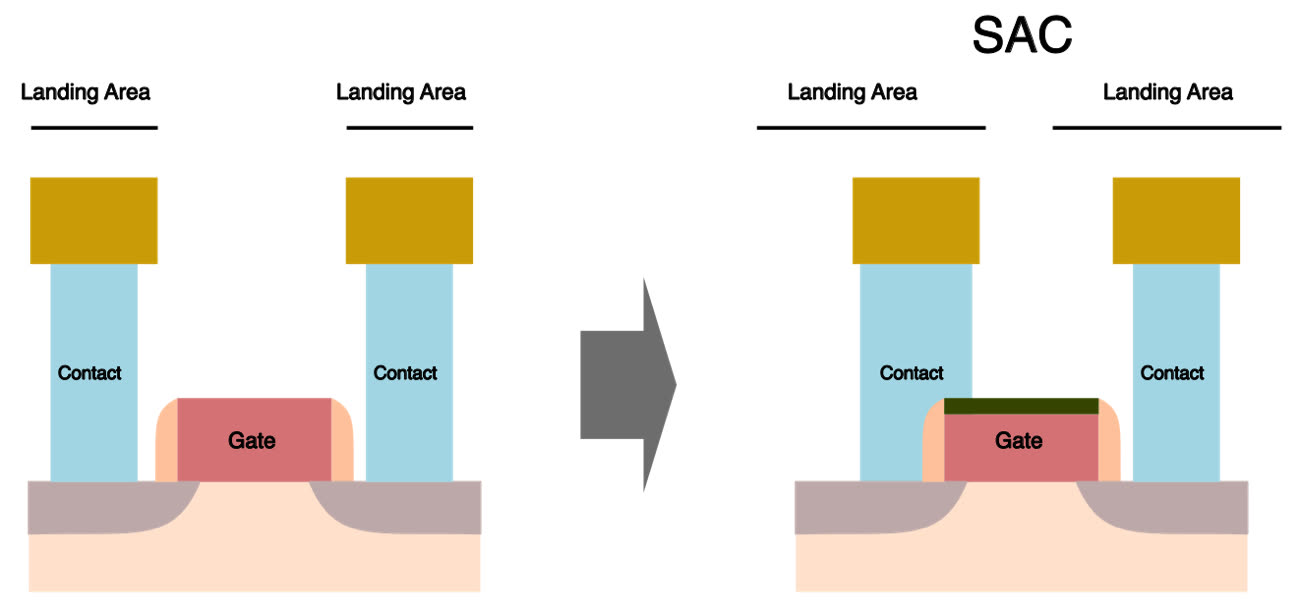

Le premier point important est que TSMC passe enfin au SAC (Self-Aligned Contact). La page de Wikichip l’explique plus en détail, mais l’idée est de fournir un peu de marge au niveau de l’alignement des composants, pour améliorer le rendement. De façon schématique, la grille d’un transistor est placée entre deux contacts, dans un espace qui diminue avec le temps. Dans le processus N3, l’espace en question est de 45 nm, ce qui est vraiment très petit… mais montre à quel point l’expression « gravure à 3 nm » est trompeuse.

L’image de WikiChip le montre, le SAC permet une marge dans l’alignement sans rendre la puce inutilisable.

L’image de WikiChip le montre, le SAC permet une marge dans l’alignement sans rendre la puce inutilisable.Dans un procédé normal, le moindre problème d’alignement risque de créer une connexion entre la grille et un des contacts, ce qui rend le transistor inutilisable. Le SAC consiste à placer un matériau diélectrique sur la grille, ce qui offre un peu de marge dans l’alignement et évite les pertes (ou augmente le rendement, selon le point de vue). Intel emploie cette technique depuis la gravure en 22 nm, Samsung l’a implémenté avec son procédé en 7 nm et TSMC y passe donc avec le 3 nm.

10 nm, 7 nm, 5 nm : la finesse de gravure, enjeu du monde mobile

Ce que permet la réduction de la taille des transistors

Avant de passer à l’analyse du N3E, il faut rappeler ce que permet la réduction de la taille des transistors. D’un point de vue purement pratique, il est d’abord possible de faire ce qu’on nomme un die shrink. L’idée est simple : vous prenez une puce gravée dans un processus et vous la passez dans le processus suivant. C’est un rien plus compliqué dans la pratique, mais l’idée est là, vous obtiendrez donc une puce plus petite avec une consommation plus faible… et c’est tout.