Ses progrès, la nouvelle puce M2 les doit en partie à une évolution de sa technologie de gravure. Comme la M1, elle est gravée en 5 nm, mais il s'agit pour elle d'un procédé de gravure 5 nm de seconde génération, qui est amélioré. TSMC, qui produit les puces conçues par Apple, ne compte pas s'arrêter en si bon chemin.

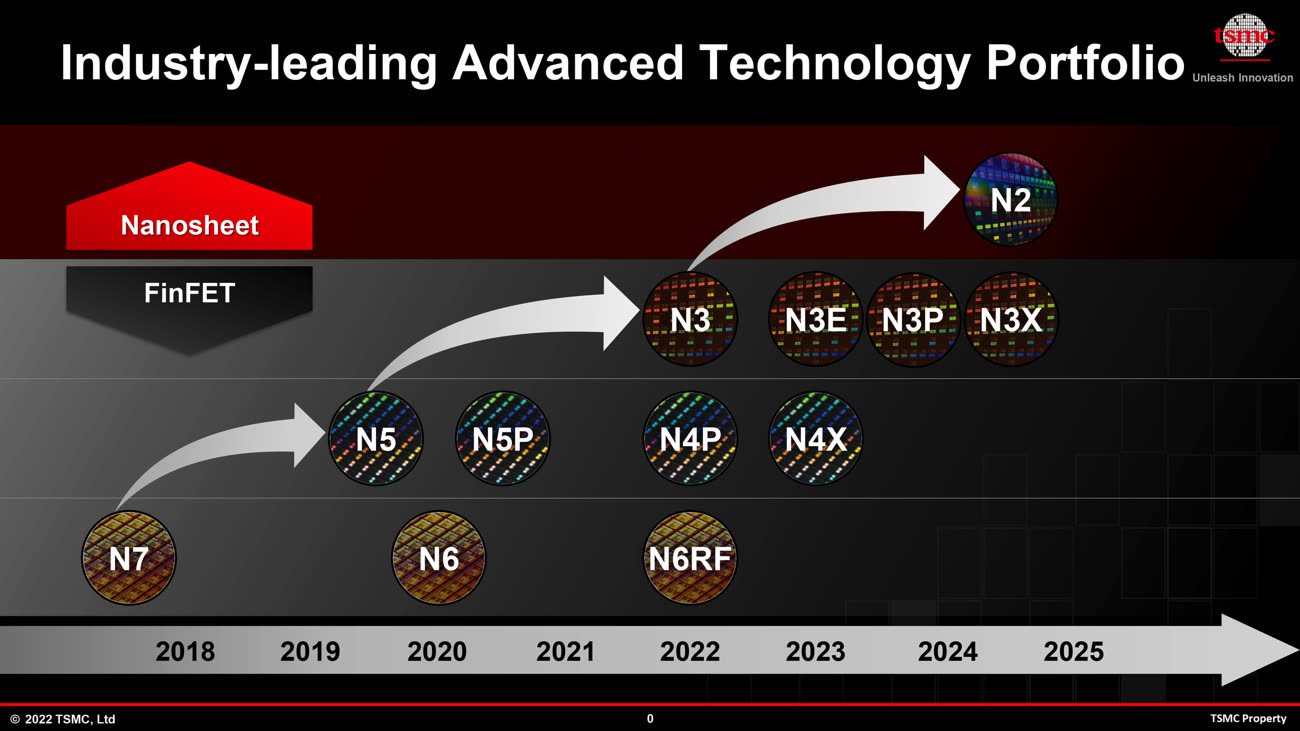

À l'occasion de son Technology Symposium, le fondeur le plus important de l'industrie a dévoilé sa feuille de route pour les prochaines années. Les procédés de fabrication devenant de plus en plus complexes, l'écart entre deux paliers va s'allonger. Il faudra environ deux ans et demi pour passer de la gravure en 5 nm vers celle en 3 nm, puis trois ans pour mettre en route la gravure en 2 nm. TSMC ne va pas rester les bras croisés pendant ce temps : comme il le fait actuellement avec la seconde génération de 5 nm, il y aura des optimisations apportées au 3 nm avant que n'émerge le 2 nm.

La gravure de masse en 3 nm, nommée N3 dans sa première version, débutera au second semestre. À temps pour la puce A16 de l'iPhone 14 Pro alors ? Peut-être pas. Comme une précédente analyse le pointait, le timing pourrait être trop juste. TSMC communique sur des puces 3 nm intégrées à des produits finaux début 2023. L'A16 pourrait se contenter du 5 nm, voire du 4 nm (N4P). Quoi qu'il en soit, si Apple ne tire pas parti du 3 nm pour l'A16, elle en profitera pour une future puce.

Par rapport à la gravure en 5 nm de première génération (puces A14, A15 et M1), le N3 devrait apporter un gain de performances de 10 à 15 % à consommation égale ou une réduction de la consommation de 25 à 30 % à performances égales. La densité logique sera, elle, réduite de 42 %, ce qui signifie que plus de transistors pourront être casés dans le même espace. TSMC va ensuite optimiser cela avec les procédés N3E, N3P, N3S et N3X de 2023 jusqu'en 2025.

Un aspect important des nœuds N3 sera la nouvelle technologie FinFlex. Pour résumer très brièvement, cette technologie permettra aux concepteurs de puces de personnaliser plus profondément leur architecture afin d'adapter très précisément la puissance, la consommation et la surface.

Après les N3 viendra le N2. Par rapport au N3E (c'est le point de comparaison donné par TSMC), ce premier nœud de gravure en 2 nm promet un gain de performances de 10 à 15 % à consommation égale, ou une réduction de la consommation de 25 à 30 % à performances égales. Les premiers produits intégrant des puces gravés en 2 nm sont prévus le second semestre 2025.

Source :