À tant comparer l’architecture ARM64 de la puce Apple M1 à l’architecture x86-64 des processeurs Intel et AMD, on oublierait presque les jeux d’instruction concurrents, comme MIPS et RISC-V. Or Micro Magic, une petite entreprise californienne, assure avoir conçu un processeur RISC-V plus efficace que les puces AMD Ryzen et Apple M1.

RISC-V a été conçue par la faculté d’informatique de l’Université de Californie à Berkeley comme une architecture de jeu d’instruction (ISA) moderne, ouverte, et praticable. Moderne, parce qu’elle abandonne quelques vieux concepts des architectures x86 et ARM. Ouverte, parce qu’elle n’impose ni licences restrictives ni redevances. Praticable enfin, parce qu’elle est destinée à l’industrialisation.

Après dix ans d’existence, force est de constater que ces trois objectifs sont remplis. La création de la RISC-V Foundation en 2015, après la publication d’une seconde version beaucoup plus robuste de l’ISA, en témoigne. Google, AMD, Qualcomm, IBM, Nvidia, Western Digital, parmi une centaine de membres, soutiennent le développement de l’architecture RISC-V.

Vous avez acheté un disque Western Digital ou Seagate ? Une carte graphique Nvidia ? Une carte de développement Arduino Cinque ? Un gadget connecté à trois francs six sous ? Alors vous avez, sans le savoir, utilisé des microcontrôleurs RISC-V. Reste maintenant à prouver que cette ISA peut rivaliser avec les architectures x86 et ARM dans la conception de processeurs généralistes.

C’est précisément ce que veut démontrer Micro Magic, une petite entreprise californienne à l’histoire tourmentée. Fondée en 1995 par Mark Santoro et Lee Tavrow, deux ingénieurs ayant notamment travaillé sur les mémoires SRAM et l’architecture SPARC pour le compte de Sun Microsystems, Micro Magic a disparu cinq ans plus tard avec son acquisition par Juniper Networks.

Les cofondateurs ont repris la marque pour créer une nouvelle entreprise, qui développe des logiciels de conception de processeurs depuis 2004. Son annonce est d’autant plus surprenante qu’elle tient en trois phrases et deux citations. Mark Santoro explique :

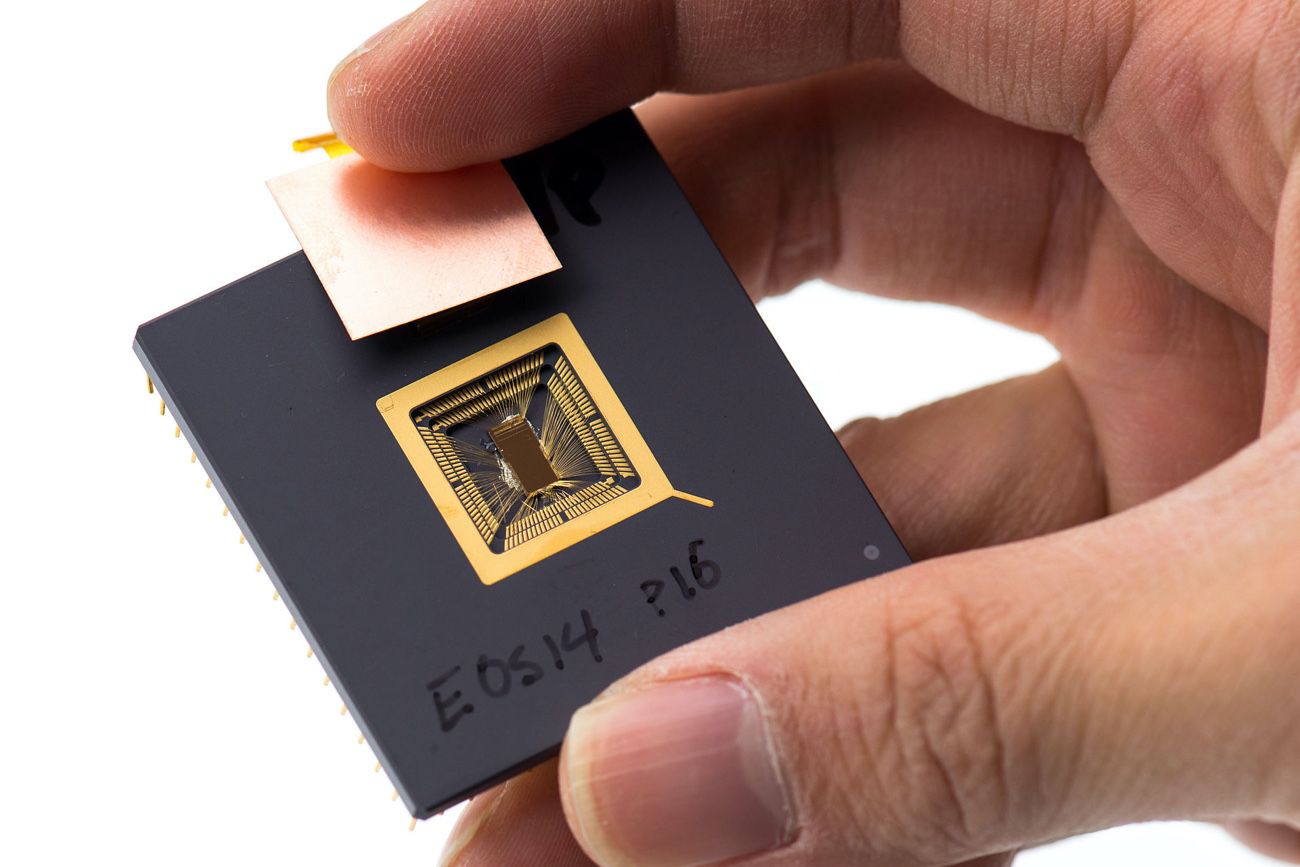

Après avoir conçu la puce RISC-V la plus rapide à 5 GHz et 13 000 CoreMarks, nous avons franchi une nouvelle étape en produisant plus de 8 000 CoreMarks à 3 GHz en consommant moins de 70 mW.

Micro Magic assure donc avoir obtenu le meilleur rapport performance/puissance jamais atteint par une puce RISC-V 64 bits, à 110 000 CoreMarks par watt. Ce que cela signifie ? CoreMark est un test synthétique de performances mis au point par l’EEMBC, une association regroupant les principaux acteurs du monde de l’informatique embarquée, dont Intel et ARM.

Nous parlons donc d’un test délibérément simplifié, taillé pour les microcontrôleurs, sans commune mesure avec les tests plus généralistes. Andy Huang, conseiller technique de Micro Magic, ose pourtant la comparaison : « une revue rapide des processeurs existants entre 3 et 5 GHz montre que le cœur RISC-V de Micro Magic est dix fois meilleur que n’importe quelle autre implémentation CISC/RISC/MIPS. »

Cette comparaison entre un simple microcontrôleur et des systèmes sur puce complexes est pourtant périlleuse. Ainsi, lorsqu’il déclare à EETimes que « la puce M1 équivaut grossièrement à 10 000 CoreMarks » et qu’il suffit de « diviser cela par huit cœurs et 15 W » pour obtenir un rapport performance/puissance inférieur à 100 CoreMarks par watt, il ajoute de la désinformation à la confusion.

Les huit cœurs de la puce M1 ne sont pas égaux, un cluster de quatre cœurs utilisant la microarchitecture FireStorm optimisée pour les performances, et un autre cluster de quatre cœurs utilisant la microarchitecture IceStorm optimisée pour l’efficacité énergétique. Le premier cluster utilise dix fois plus d’énergie que le deuxième !

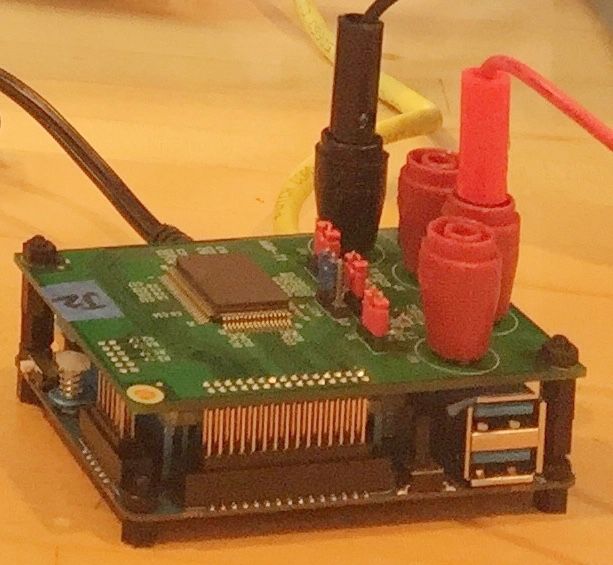

En lisant de près les deux phrases du communiqué de Micro Magic, on comprend qu’elle sort seulement d’une phase de « simulation » avec ses logiciels, avec une première « puce de démonstration ». Cette annonce très préliminaire vise essentiellement à attirer l’intérêt… et les capitaux.

Bref, ce résultat est intrigant, mais loin de constituer une preuve définitive. Une chose est sure : le succès de l’architecture RISC-V ne se dément pas. Après Western Digital, Seagate annonce avoir créé deux microcontrôleurs RISC-V, dont l’un a déjà « prouvé sa fonctionnalité dans les disques durs ». L’architecture ARM est sous le feu des projecteurs, mais l’architecture RISC-V creuse son trou.