Inexistant dans les smartphones et maintenant concurrencé dans les serveurs par Amazon et Google qui créent eux-mêmes les puces dont ils ont besoin, Intel a fait deux annonces importantes qui doivent lui permettre de « toucher de nouveaux marchés ».

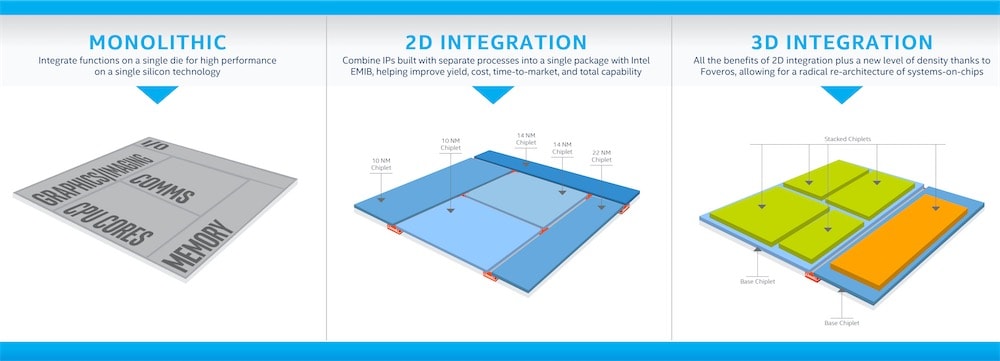

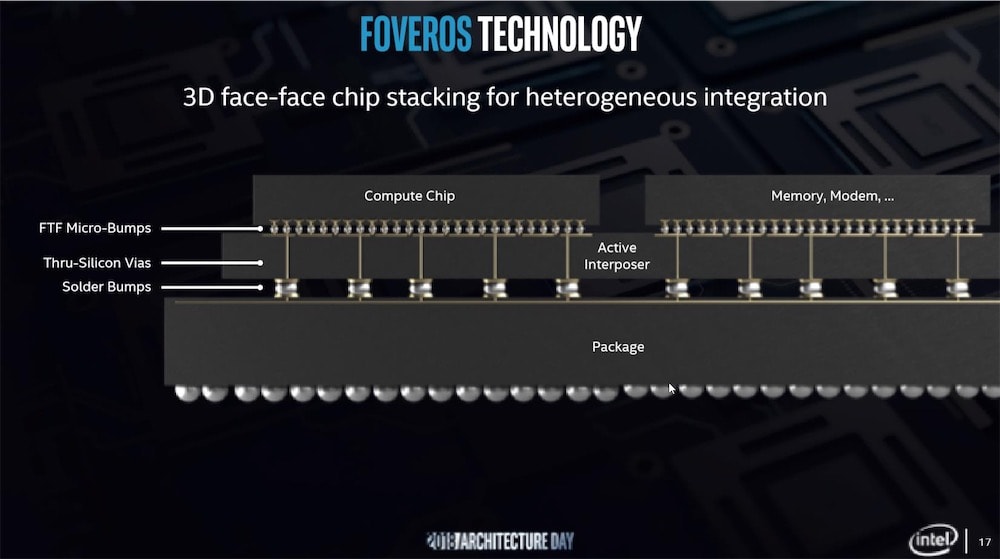

Premièrement, le fondeur a mis au point une nouvelle technologie, nommée Foveros, permettant de fabriquer des puces plus modulaires. Plutôt que de former un tout nécessairement gravé avec un procédé unique, les puces pourront être divisées en autant de « chiplets » que de fonctions principales.

Une puce Foveros pourra ainsi être composée d’un CPU gravé en 10 nm pour des performances maximales, ainsi que d’une partie dédiée aux entrées/sorties produite en 14 ou même 22 nm avec un procédé spécial basse consommation.

« Les meilleurs transistors pour un CPU de bureau ne sont pas forcément les meilleurs pour un GPU. De même, vous avez besoin de transistors différents pour la 5G et les autres connectiques », a expliqué à Wired Raja Koduri, l’ancien architecte des cartes graphiques d’AMD qui est devenu architecte en chef d’Intel l’année dernière.

Deuxièmement, Intel a enfin annoncé une nouvelle architecture. Finis les innombrables « bidules Lake » et fini la gravure en 14 nm, place à Sunny Cove et au 10 nm. Destinée aussi bien aux processeurs Core qu’aux Xeon, l’architecture Sunny Cove devrait améliorer les performances sur un thread, apporter de nouvelles instructions pour accélérer certaines opérations (comme le chiffrement, la compression et le machine learning) et offrir une meilleure évolutivité.

Côté GPU, Intel vise un circuit graphique intégré capable d’atteindre le TFLOPS de puissance (en comparaison, la Radeon Pro 555 de l’iMac 4K le plus abordable a une puissance de 1,3 TFLOPS).

Les premiers processeurs Core Sunny Cove sont prévus pour le deuxième semestre. C’est à la même période que les puces à assemblage Foveros arriveront. Si Intel a d’ores et déjà annoncé qu’il y aura des puces Foveros équipées de l’architecture Sunny Cove, les deux ne seront pas forcément liés.